www.digiembedded.com

297

System Control Module

The Miscellaneous System Configuration and Status register configures miscellaneous

system configuration bits.

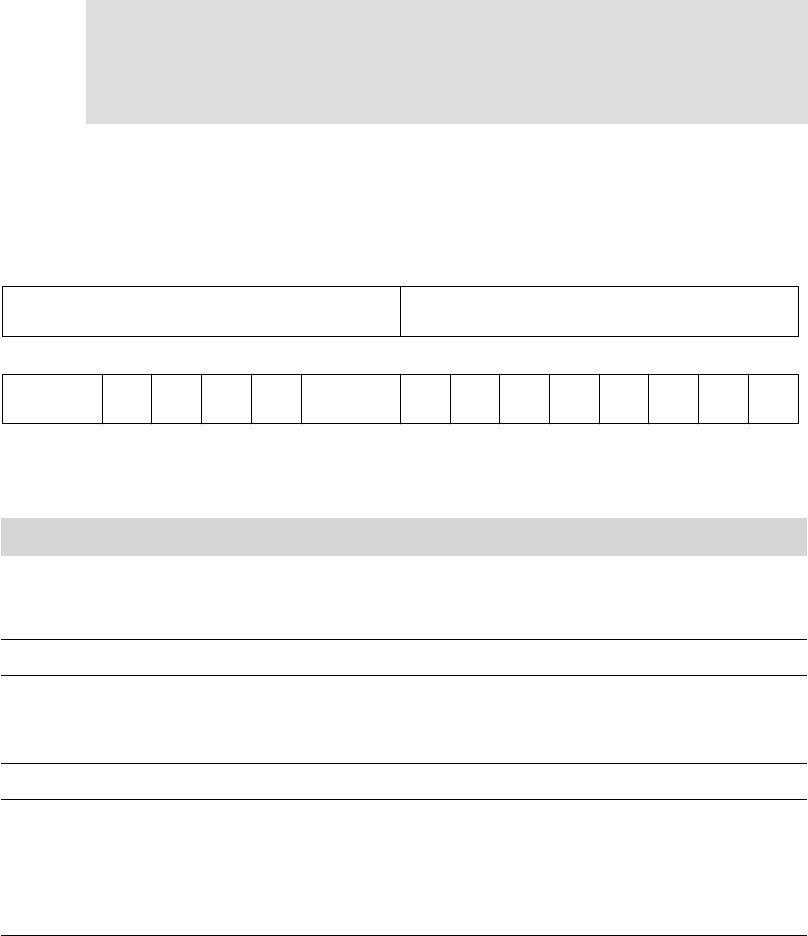

Register bit assignment

Bits Access Mnemonic Reset Description

D31:24 R REV 0x0 Revision

Indicates the NS9750 hardware identification and

revision.

D23:14 N/A Reserved N/A N/A

D13 R PCIA 0x1 PCI arbiter configuration

0 External PCI arbiter

1 Internal PCI arbiter

D12 N/A Reserved N/A N/A

D11 R BMM

HW strap

reset_done

Bootup memory mode

0 Boot from SDRAM using SPI serial EEPROM

1 Boot from Flash/ROM on memory chip

select 1

Status only; indicates the bootup process.

D10 R CS1DB

HW strap

boot_strap[

0]

Chip select 1 data byte lane configuration HW strap

setting

Status bit indicating the hardware strap setting of

external memory chip select 1 byte lane/write enable

signal configuration. This configuration can be changed

by writing to the appropriate control register in the

memory controller.

Table 187: Miscellaneous System Configuration and Status register

PCIA Rsvd CS1DBBMM CS1DW MCCM PMSS CS1P Rsvd ENDM MBAR Rsvd IRAM0

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

REV Reserved

Reserved