Static memory controller

134

NS9750 Hardware Reference

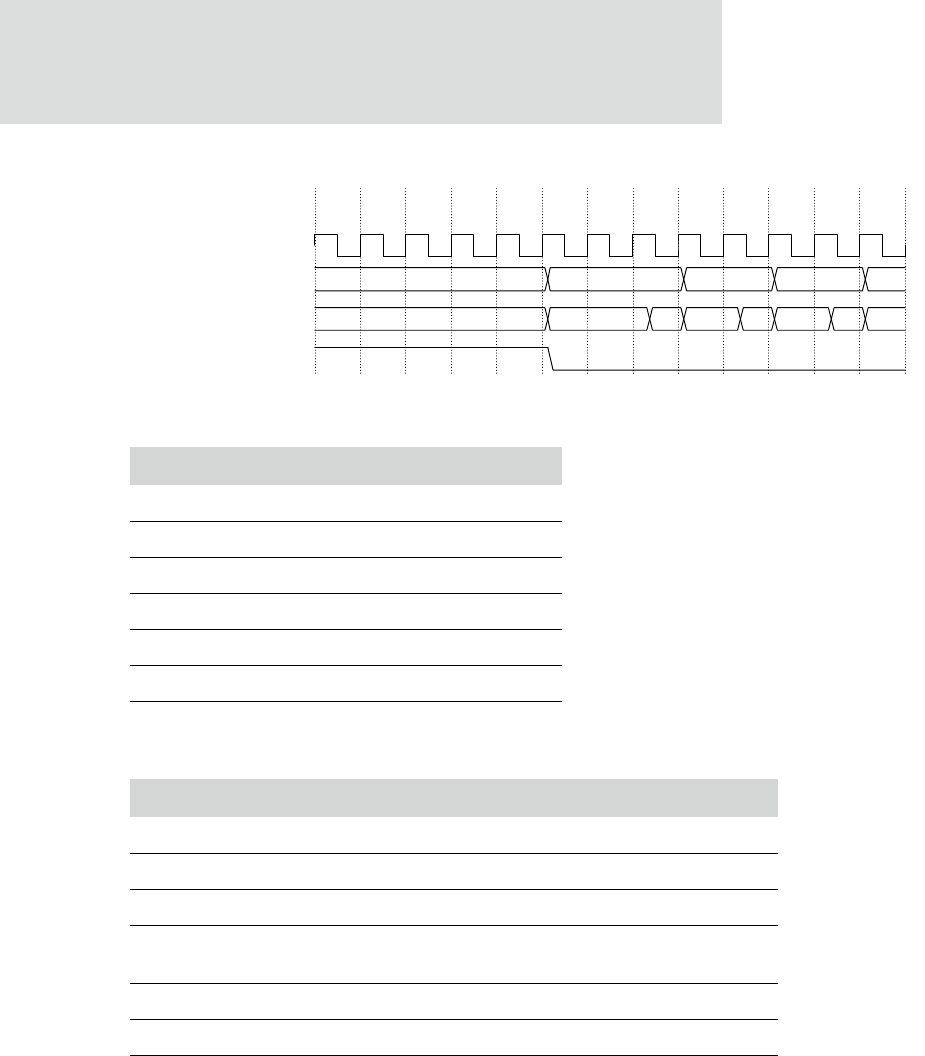

Figure 47: External memory page mode read transfer timing diagram

Timing parameter Value

WAITRD 2

WAITOEN 0

WAITPAGE 1

WAITWR N/A

WAITWEN N/A

WAITTURN N/A

Table 61: Static memory timing parameters

Cycle Description

T0 AHB address provided to memory controller.

T0-T1 AHB transaction processing.

T1-T4 Arbitration of AHB memory ports.

T4-T5 Static memory transfer 0, address, chip select, and control signals

submitted to static memory.

T5-T6 Read wait state 1.

T6-T7 Read wait state 2.

T7-T8 Read data 0 returned from static memory.

Read data is provided to the AHB.

Static memory transfer 1, address, chip select, and control signals

submitted to static memory.

Table 62: External memory page mode read

ADDR

DATAIN

SCTSOUT_n

OEOUT_n

A A+4

D(A)

D(A+4) D(A+8)

A+8

clk_out

T0 T1 T2 T3 T4 T5 T6 T7 T12T10 T11T8 T9