DEFINITY Enterprise Communications Server Release 5

Maintenance and Test for R5vs/si

555-230-123

Issue 1

April 1997

Maintenance Object Repair Procedures

Page 10-1183PROCR (Processor Circuit Pack)

10

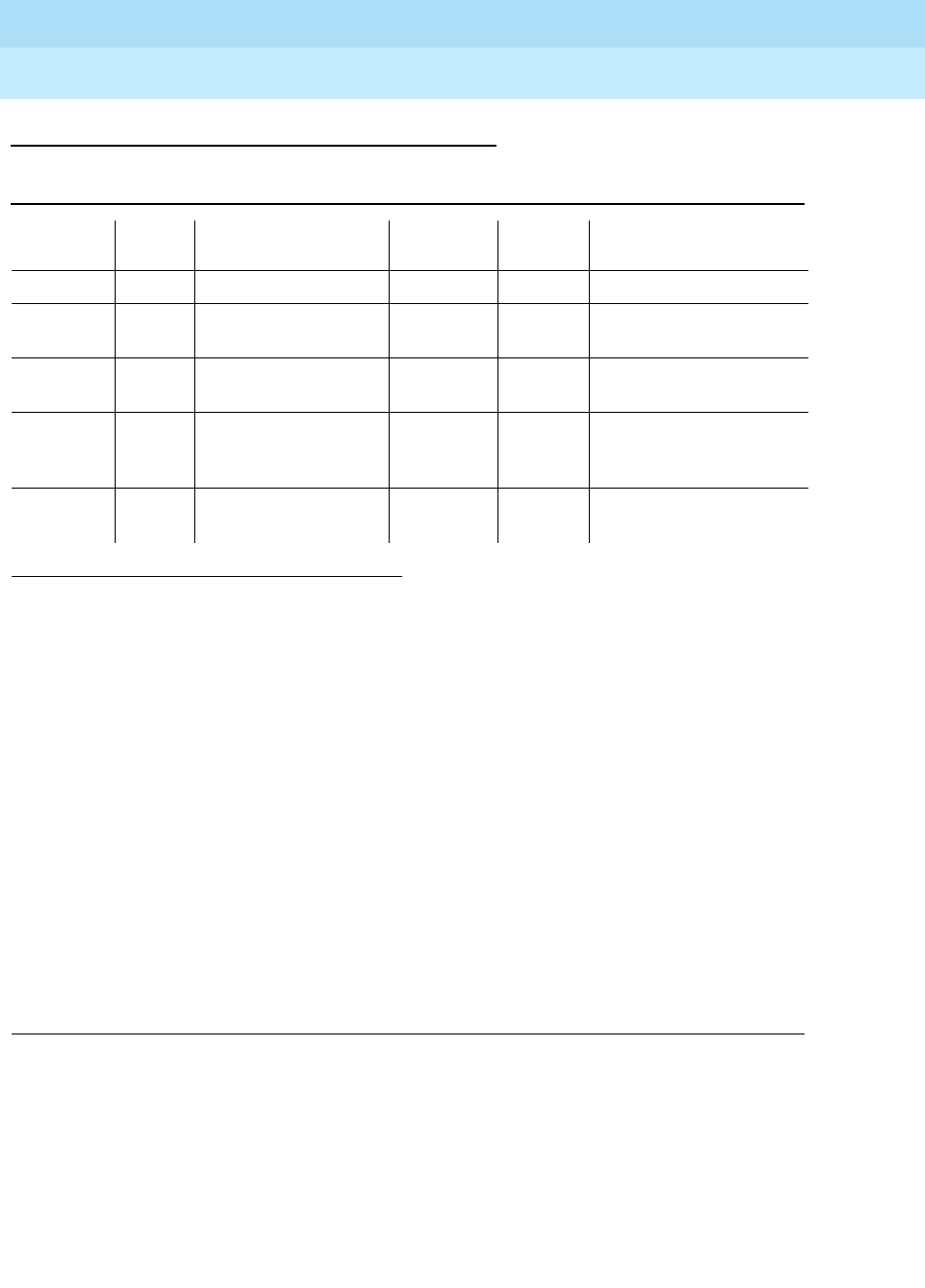

Error Log Entries and Test to Clear Values

Notes:

a. The Software Initiated Interrupt Test (#77) failed. Refer to the FAIL

condition of this test for further action.

b. The ROM Checksum Test (#80) failed. Refer to the FAIL condition of this

test for further action.

c. The Processor Non-maskable Interrupt Test (#82) failed. Refer to the FAIL

condition of this test for further action.

d. The Processor Sanity Timer Test (#83) failed. Refer to the FAIL condition of

this test for further action.

1. Software does not accept the repeat option on the TN773 circuit pack [G3iV1.1-286]. The repeat

option is valid only on the TN786B circuit pack. You must manually repeat the command with the

long option the designated number of times from the administration terminal and from a remote SAT

because the Sanity Timer Test (#83) logs you off. In G3iV1.1-286, if the test processor long System

Technician command is executed six times back-to-back, the system goes into SPE-DOWN mode.

2. Run the Short Test Sequence first. If all tests pass, run the Long Test Sequence. Refer to the

appropriate test description and follow the recommended procedures.

Table 10-361. 80286/386 Processor Circuit Pack Error Log Entries

Error

Type

Aux

Data Associated Test

Alarm

Level

On/Off

Board Test to Clear Value

1

0

2

0 Any Any Any test processor a/b r 1

1 (a) 0 Software Initiated

Interrupt Test (#77)

MAJOR ON test processor a/b r 3

769 (b) 0 ROM Checksum Test

(#80)

MAJOR ON test processor a/b r 5

1025 (c) 0 Processor

Non-maskable

Interrupt Test (#82)

MAJOR ON test processor a/b r 2

1281 (d) 0 Processor Sanity

Timer Test (#83)

MAJOR ON test processor a/b l r 2