DEFINITY Enterprise Communications Server Release 5

Maintenance and Test for R5vs/si

555-230-123

Issue 1

April 1997

Maintenance Object Repair Procedures

Page 10-1193PROCR (TN790 RISC Processor Circuit Pack)

10

Processor Bus Time-out Exception Test (#82)

This test is a nondestructive test. The test is used to verify that the RISC

Processor can intentionally cause a BUS TIMEOUT EXCEPTION (BTE) and then

verifies if it vectors to the correct interrupt routine. This is basically a test of the

internal operation of the RISC Processor chip and the bus time-out circuitry.

Processor Cache Test (#895)

This test is a nondestructive test. This test overwrites the contents in the

Instruction and Data Caches, requiring them to be refilled during normal

execution.

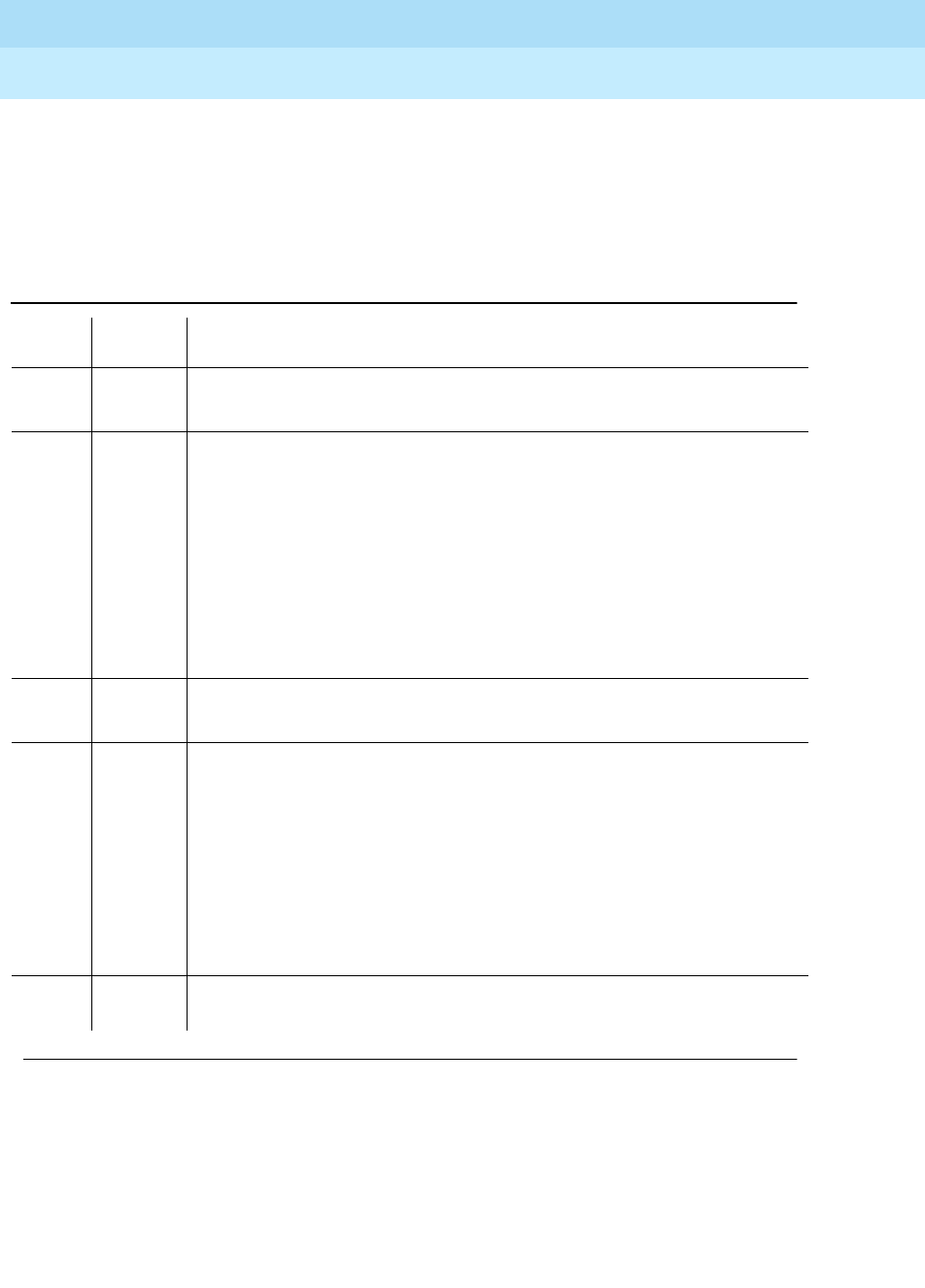

Table 10-368. Test #82 Processor Bus Time-out Exception Test

Error

Code

Test

Result Description/ Recommendation

100 ABORT The test did not complete within the allowable time period.

1. Retry the command.

1029

2014

2015

2016

2017

2018

2020

2022

2024

2025

2051

ABORT Refer to STBY-SPE for a description of these error codes.

2500 ABORT Internal system error

1. Retry the command.

FAIL The interrupt was not detected or acted upon.

1. Repeat the command at 1-minute intervals a maximum of 5 times.

2. If the test continues to fail, the Processor circuit pack should be

replaced. The replacement must have enough memory for this system.

3. If replacement of the Processor circuit pack still results in test failure, the

following circuit packs should be replaced, one at a time in the order

provided: TN765 Processor Interface, TN777B Network Control, TN778

Packet Control, and TN772 Duplication Interface circuit packs. The test

should then be repeated.

PASS The interrupt was correctly detected. The RISC Processor is functioning

correctly.

Continued on next page