DEFINITY Enterprise Communications Server Release 5

Maintenance and Test for R5vs/si

555-230-123

Issue 1

April 1997

Maintenance Object Repair Procedures

Page 10-1274STBY-SPE (Standby SPE)

10

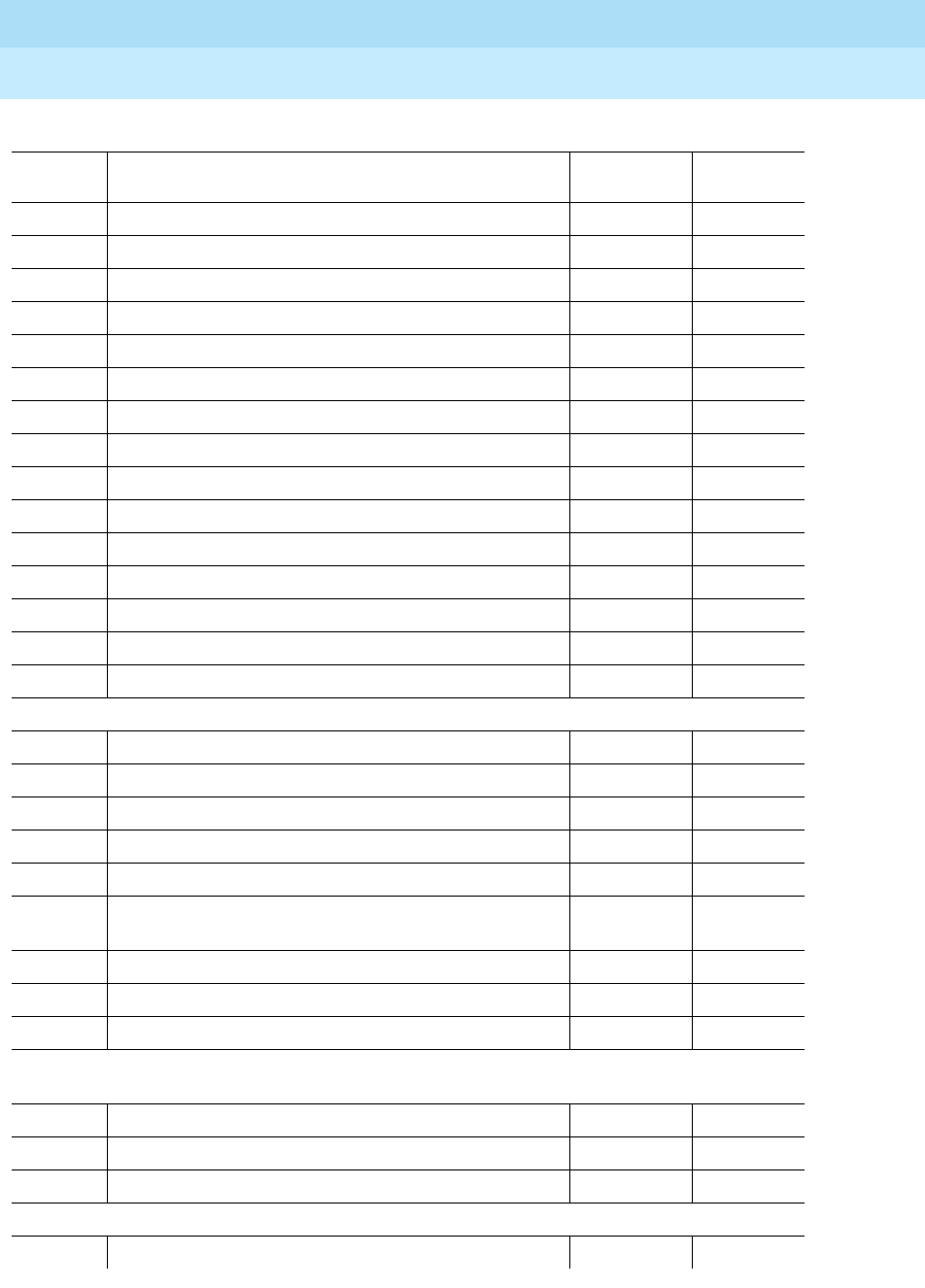

95 Time-of-Day Clock Test (SW-CTL) X X

92 Control Channel Interface Test (SW-CTL) X X

94 Control Channel Transmission Test (SW-CTL) X X

324 EPN Maintenance Board Interface Test (SW-CTL) X X

77 Processor Software Initiated Interrupt Test (PROCR) X X

80 Processor ROM Checksum Test (PROCR) X X

82 Processor Non-Maskable Interrupt Test (PROCR) X X

83 Processor Sanity Timer Test (PROCR) X

102 MTP Outpulse Relay Test (PR-MAINT) X X

103 MTP Analog Loop Around Test (PR-MAINT) X X

106 MTP Sanity Handshake Test (PR-MAINT) X X

228 MTP Manager I Channel Loop Around Test (PR-MAINT) X X

229 MTP Auxiliary Channel Loop Around Test (PR-MAINT) X X

101 MTP Reset Test (PR-MAINT) X

104 MTP Dual Port RAM Test (PR-MAINT) X

The following Memory Card and 12 Volt Power Supply tests are executed:

701 12 Volt Power Supply Test (12V-PWR) X X

695 Cartridge Insertion Test (CARD-MEM) X X

696 Cartridge Format and Read Test (CARD-MEM) X X

697 Cartridge Match Test (CARD-MEM) X X

698 Cartridge Write-Protected Test (CARD-MEM) X X

699 Cartridge Directory Sanity Check and Recovery Test

(CARD-MEM)

XX

694 Cartridge Translation Data Integrity Test (CARD-MEM) X

693 Cartridge Erase/Write/Read Test (CARD-MEM) X

703 Flash Data Consistency Test (FL-DATA) X

For each Processor Interface circuit pack in the Standby SPE, the following PI-BD tests are

run:

52 Control Channel Test (PI-BD) X X

50 NPE Audit (PI-BD) X

423 Standby PI Board Test (PI-BD) X X

For each administered Processor Interface Port, the following test is run:

404 Standby PI Port Test (PI-PT) X X

Test Sequence of Test SPE-Standby Command

Test

Number Name of Test and Associated MO

Short Test

Sequence

Long Test

Sequence